## Exploring Extreme Fine-grained Parallelism on Modern Many-Core Architectures

### PhD Proposal

at Illinois Institute of Technology at the Department of Computer Science Data Intensive Distributed Systems Laboratory

#### **Committee Members**

Ioan Raicu Robert Harrison Jia Wang Kyle Hale Stefan Muller

| Primary Advisor:<br>Advisor: | Dr. Ioan Raicu<br>Dr. Robert J. Harrison (Stony Brook University)                          |

|------------------------------|--------------------------------------------------------------------------------------------|

| Author:                      | Poornima Nookala<br>10 W 31st Street, Chicago IL<br>60616 Chicago<br>pnookala@hawk.iit.edu |

| Submission:                  | 6th May 2022                                                                               |

Copyright © 2022 Poornima Nookala All rights reserved.

#### Abstract

Processors with 100s of threads of execution and GPUs with 1000s of cores are among the state-of-the-art in high-end computing systems. This transition to many-core computing has required the community to develop new algorithms to overcome significant latency bottlenecks through massive concurrency. Implementing efficient parallel runtimes that can scale up to hundreds of threads with extremely fine-grained tasks (less than  $\sim$ 100  $\mu$ s) remains a challenge. We propose XQueue, a novel lockless concurrent queueing system that can scale up to hundreds of threads. We integrate XQueue into LLVM OpenMP and implement X-OpenMP, a library for lightweight tasking on modern many-core systems with hundreds of cores. We show that it is possible to implement a parallel execution model using lock-less techniques for enabling applications to strongly scale on many-core architectures. While OpenMP is suitable for on-node parallelism, it is crucial to support heterogenous architectures and distributed memory environments. The existing parallel programming environments that support distributed memory environments either discover the DAG entirely on all processes which limits the scalability or introduce explicit communications which increases the complexity of programming. We implement Template Task Graph (TTG), a novel programming model and its C++ implementation by marrying the ideas of control and data flowgraph programming. TTG supports compact specification and efficient distributed execution of dynamic and irregular applications. TTG can address the issues mentioned above without sacrificing scalability or programmability by providing higher-level abstractions than conventionally provided by task-centric programming systems, but without impeding the ability of these runtimes to manage task creation and execution as well as data and resource management efficiently. TTG implementation currently supports distributed memory execution over 2 different task runtimes PaRSEC and MADNESS.

## Contents

| 1 | Intro | ductior | ۱                                                   | 1  |

|---|-------|---------|-----------------------------------------------------|----|

|   | 1.1   | Early   | Work in Many Task Computing                         | 3  |

|   | 1.2   | Summ    |                                                     | 6  |

| 2 | How   | Bad Is  | Concurrent Queue Performance Across Many Threads?   | 7  |

|   | 2.1   | Baseli  | ne Queue Performance                                | 7  |

|   | 2.2   | Analys  | sis of Synchronization Mechanisms                   | 12 |

|   |       | 2.2.1   | Tesbed, Software Stack, and Timing Mechanisms       | 12 |

|   |       | 2.2.2   | Performance of Synchronization Mechanisms           | 13 |

|   | 2.3   | Conclu  | usion                                               | 15 |

| 3 | Scal  | able Co | oncurrent Queues on Modern Many-core Architectures  | 17 |

|   | 3.1   | Load b  | palancing                                           | 19 |

|   | 3.2   | Xtask   | - eXtreme fine-grained TASKing runtime              | 20 |

|   | 3.3   | XQue    | ue Integration with the OpenMP Runtime              | 21 |

|   | 3.4   | Perfor  | mance Evaluation                                    | 22 |

|   |       | 3.4.1   | Experiment Setup                                    | 22 |

|   |       | 3.4.2   | Micro-benchmark Performance Results                 | 23 |

|   |       | 3.4.3   | Macro-benchmark Performance Results                 | 25 |

|   | 3.5   | Conclu  | usion                                               | 30 |

| 4 | X-O   | penMP   | - eXtreme fine-grained tasking using lock-less work |    |

|   | stea  | ling    |                                                     | 31 |

|   | 4.1   | Motiva  | ation                                               | 32 |

|   | 4.2   | X-Ope   | enMP - eXtreme fine-grained tasking runtime         | 34 |

|   |       | 4.2.1   | Load Balancing                                      | 34 |

|   | 4.3   | Evalua  | ation                                               | 41 |

|   |       | 4.3.1   | Microbenchmarks                                     | 42 |

|   |       | 4.3.2   | Macrobenchmarks                                     | 45 |

|   |       | 4.3.3   | Results Discussion and Summary                      | 52 |

|    | 4.4                                                           | Conclu                                                         | usion                                                   | 53 |

|----|---------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------|----|

| 5  | The Template Task Graph (TTG) — an emerging practical dataflo |                                                                |                                                         |    |

|    | prog                                                          | gramming paradigm for scientific simulation at extreme scale 5 |                                                         |    |

|    | 5.1                                                           | TESS                                                           | E - Task-based Environment for Scientific Simulation at |    |

|    |                                                               | Extrer                                                         | ne Scale                                                | 55 |

|    | 5.2                                                           | Templ                                                          | ate Task Graph                                          | 57 |

|    |                                                               | 5.2.1                                                          | TTG Concepts                                            | 58 |

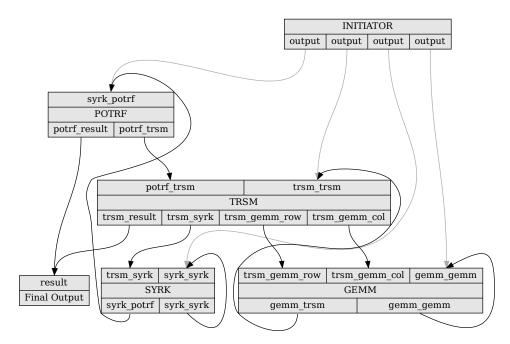

|    |                                                               | 5.2.2                                                          | Cholesky Decomposition Example Using TTG                | 60 |

|    |                                                               | 5.2.3                                                          | Sending and Broadcasting                                | 63 |

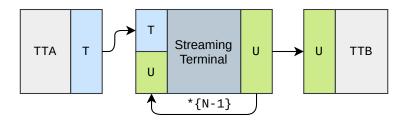

|    |                                                               | 5.2.4                                                          | Streaming Terminals                                     | 64 |

|    |                                                               | 5.2.5                                                          | Data serialization                                      | 65 |

|    |                                                               | 5.2.6                                                          | TTG Execution Backends                                  | 66 |

|    | 5.3                                                           | Bench                                                          | ımarks                                                  | 68 |

|    |                                                               | 5.3.1                                                          | Test Setup                                              | 69 |

|    |                                                               | 5.3.2                                                          | Dense Cholesky Factorization                            | 69 |

|    |                                                               | 5.3.3                                                          | Floyd-Warshall All-Pairs-Shortest Path (FW-APSP)        | 71 |

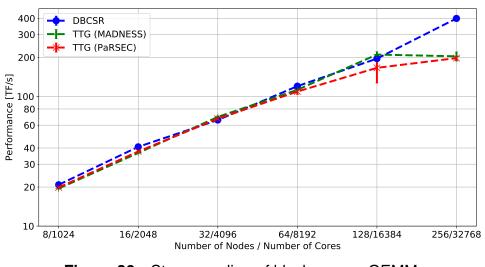

|    |                                                               | 5.3.4                                                          | Block-Sparse GEMM                                       | 74 |

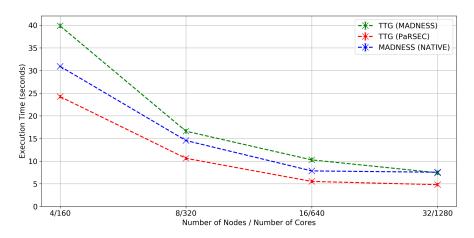

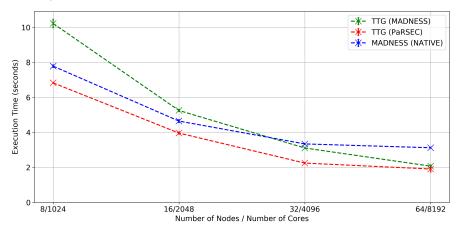

|    |                                                               | 5.3.5                                                          | Multi-Resolution Analysis (MRA)                         | 77 |

|    | 5.4                                                           | Concl                                                          | usion                                                   | 80 |

| 6  | Rela                                                          | ated Wo                                                        | ork                                                     | 81 |

|    | 6.1                                                           | Many                                                           | Task Computing                                          | 81 |

|    | 6.2                                                           | Concu                                                          | irrent queues                                           | 82 |

|    | 6.3                                                           | Paralle                                                        | el runtime systems                                      | 83 |

|    | 6.4                                                           | Load I                                                         | Balancing                                               | 84 |

|    | 6.5                                                           | Flowg                                                          | raph Programming                                        | 85 |

| 7  | Con                                                           | clusion                                                        | and Future Work                                         | 86 |

| Re | eferer                                                        | nces                                                           |                                                         | V  |

## CHAPTER 1

#### Introduction

The Department of Energy (DOE) has reported that "Scientific productivity is one of the top ten exascale research challenges [69]". The scientific computing community is facing unprecedented changes in computer architectures that has fueled the emergence of the many-core computing architecture. Processors with 100s and GPUs with 1000s of threads of execution are among the state-of-the-art in high-end computing systems. In a recent report [50], the DOE stated that "the transition of applications to exploit massive on-node concurrency... create the most challenging environment for developing applications in at least two decades." Extreme on-node concurrency levels of order  $10^4$  is required in order to achieve exascale performance levels according to this report. They continued by saying "much of the performance improvement must come from vectorization and lightweight tasking." These heterogeneous systems provisioned with many-core accelerators fundamentally make programmability harder as we shift from MIMD (multiple instruction, multiple data) programming to a mixture of MIMD and SIMD (single instruction, multiple data) programming. The era of manycore and exascale computing will bring new fundamental challenges in how we build large-scale systems, how we manage them, and how we program them. The techniques that have been designed decades ago will have to be dramatically changed to support the coming wave of extreme-scale general purpose parallel computing.

1

Today, the increase in performance for single-threaded processor has come to an end due to the limitation of the current Very Large Scale Integration (VLSI) technology. In response, most hardware companies are designing and developing new parallel architectures [40]. To achieve higher performance, applications need to leverage the parallelism on modern architectures. On the other hand, multicore designs are also encountering scaling problems, notably the "Dark Silicon" phenomenon [37]. Power and cooling concerns suggest the number of dynamically active transistors on a single die may be greatly constrained in the near future. In other words, even if the number of transistors per chip continues to follow Moore's law, we will not be able to use all of them simultaneously. This problem may lead to scenarios in which only a small percentage of the chip's transistors can be "on" at a time [98]. The limitations of current CMOS technology has fueled the emergernce of many-core architectures and many of these massively parallel platforms offer a high ratio performance/cost and an efficient power consumption design [109, 112, 108]. They are also widely used in high performance computing, including systems ranging from a cluster of personal computers, to large scale supercomputers. As per the Top 500 list [102], many of the most powerful supercomputers today are based on platforms that combine multicore and manycore processors with data parallel accelerators.

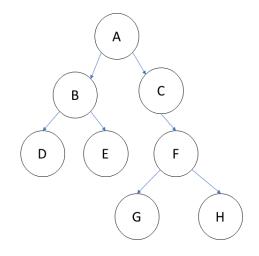

Task-based parallelism is a simple paradigm for shared memory parallelism in which a computation is broken-down into a set of inter-dependent tasks which can then be executed concurrently on various cores. When a task is created by some processor/thread, it is conceptually queued for execution by a future available thread. Task dependencies and/or data dependencies are used to control the flow of tasks through the runtime system. Tasks can be modeled as Directed Acyclic Graph (DAG) which can can dynamically unfold during the execution of the application. Given the DAG, tasks can be executed using a set of processors/threads where each thread dequeues a task from a queue and executes it. If the queue is empty, thread waits for a task to come in to the queue until the whole DAG is processed.

Figure 1 shows a DAG with a set of tasks with arrows showing the dependencies. Nodes at one level can ideally be executed in parallel. Here tasks D,E, G and H can be executed in parallel and they do no have dependencies since they are the leaf tasks. Once the dependencies for F have been resolved, task F can execute. The execution models of many parallel languages and libraries [84, 9, 120, 119, 38, 104] rely on such task parallelism.

Figure 1 Directed Acyclic Graph (DAG)

Most parallel runtime systems today support execution of coarse-grained tasks with very high efficiency, however when it comes to fine-grained tasks, the efficiency decreases due to the overhead of scheduling and managing the tasks. Hence, the need for low overhead tasking becomes significant in order to explore extreme parallelism from applications.

Many-Task Computing (MTC) [88] has been an emerging paradigm and area of research for some years now. An MTC workload consists of tasks that run uninterrupted from start to completion. The task duration may be highly variable, ranging from tens of cycles to hundreds and thousands of cycles. Their dependency and data-passing characteristics may range from many similar tasks to complex, and possibly dynamically determined, dependency patterns. Many-task computing differs from high throughput computing (HTC) in the context of using large number of computing resources over short periods of time to accomplish many computational tasks. To efficiently handle MTC workloads, the system needs to exploit parallelism as much as possible. As more and more cores are being added to increase the processing speed, the need for parallel execution models that can leverage full capabilities of the processors by over-decomposition of tasks into fine-grained tasks is increasing.

#### 1.1 Early Work in Many Task Computing

GPUs have a very restrictive programming model, but provide at least an order of magnitude better throughput for applications painstakingly coded to that model. To program GPUs, typically there is a need to learn another programming language such as CUDA (NVIDIA) or OpenCL (AMD). As a result,

existing vendors must spend extra time and effort to modify or rewrite parts of their codebase to take advantage of the new capabilities provided by General Purpose GPUs (GPGPUs). Besides that, barely rewriting an application just to offload computations to a GPU rarely works well. Because of the architecture of most GPUs out there, applications must be tailored from the ground up to follow the rules of the restrictive programming model of GPUs, otherwise they may suffer from severe performance penalties. Because of that, interested vendors cannot afford to go through the effort involved. Finally, while GPUs are great for massively parallel applications with threadswitching that comes almost at no cost, their performance can take a large hit when executing programs with complex logic (like complicated branching and looping for example). Therefore they may be unsuitable for certain applications of MTC. The Intel Xeon Phi is a family of processors based on the Intel MIC Architecture [56] that incorporates earlier work on the Larrabee architecture [95]. It follows an alternative programming model that, although may not provide the same level of parallelism, provides more flexibility and therefore can be more suitable for certain application of MTC that GPUs are not suited for. The reason is that the Xeon Phi has x86 cores that are more capable (can handle complex branching and looping) than most GPU cores. Another advantage of having x86 cores is that programming the coprocessor minimizes the amount of work that needs to be done in order to integrate a Xeon Phi to an existing system. That is because the Phi does not require being programmed in any specific framework and it can natively run applications written in C with Pthreads or OpenMP. This work used the 22nm Knights Corner chip, which was the first commercial product from this family. This product has been discontinued due to the problems with 10nm technology and we briefly discuss our findings from using this chip.

The Knights Corner is a PCIe vector co-processor with integrates up to 61 in-order dual issue x86 cores, which trace some history to the original Pentium core, like the Larrabee predecessor. Among other enhancements, the Corner's cores are augmented with 64-bit support, 4 hardware threads per core (resulting in more than 200 hardware threads available on a single device) and 512-bit SIMD instructions [56]. Each core has a 512KB L2 cache locally but has also access to all other L2 caches in the system through a high-speed bidirectional ring [56]. Unlike previous GPUs, the L2 cache is kept fully coherent by a global-distributed tag directory.

Due to the foundations of Intel architecture, the coprocessor can be programmed in several different ways. We implemented two different framework for handling MTC workloads - OpenMP and SCIF (Symmetric Communications Interface). SCIF is a low-level API implemented by Intel for Xeon Phis for communications across PCIe. For the OpenMP implementation, we used offloading approach for offloading computations from host to the Phi. For the SCIF part, we implemented the framework to run natively on the Phi while accepting jobs from clients running on the host CPU [6]. The major advantage of native execution coupled with SCIF over offloading is that the developer gets more control overall in the configuration and the architecture of their design in order to maximize performance. In addition, different MIC cards can communicate directly with each other basically making certain designs more efficient. The OpenMP version of the framework is developed using a Producer-Consumer architecture which communicates using shared memory for IPC. The Consumer side hosts the framework which runs as multiple worker threads which use the shared memory space as a queue structure, continuously accepting new tasks from producer. Likewise, the producer acts as a client process which submits tasks to the queue. Asynchronous offloading is used to allow the framework to be non-blocking to continue accepting tasks while other tasks are running on the Phi. After submitting the job, the clients can request the result and the server will deliver it to them when the task has finished processing. The whole procedure is non-blocking for the server who can handle multiple requests and submissions at the same time.

To analyze the performance of our implementations, we ran a simple taskbased matrix multiplication benchmark on the Midway High Performance Computing Cluster at the University of Chicago. Our testing host is an Intel SandyBridge with 16 cores at 2.6 Ghz and 32 GB of RAM. It has 2 Xeon Phis from the Knights Corner family attached to it. We calculated speedup compared to the sequential version and observed higher performance with fine-granular tasks, but the gain reduces as problem scales up to higher matrix sizes. The overheads of communication via PCIe interface quickly became evident as we scaled up the problem sizes. We also analyzed the performance of sleep(0) tasks to assess the ideal performance of Xeon Phi with very short length tasks. We achieved an efficiency of 90% with tasks lasting as short as 640 microseconds.

#### 1.2 Summary

These preliminary observations motivated us to further explore many-core architectures and fine-grained tasking with the goal to reduce the underlying overheads of the existing parallel runtime systems and to explore extreme fine-grained parallelism. Parallel execution models typically uses concurrent data structures like queues to hold a bag of tasks. We shifted our focus to analysing the performance of concurrent queues to understand the overheads of managing tasks in task-based runtime systems.

# CHAPTER 2

## How Bad Is Concurrent Queue Performance Across Many Threads?

Concurrent data structures have to deal with data synchronization and communication between threads. Synchronization mechanisms like mutexes, semaphores and spinlocks are known to have significant overhead and can easily become the bottleneck to achieving high performance. Many researchers have proposed better performing lock-free data structures using atomic instructions supported by hardware. Many programming languages like Java and C++ implement lock-free data structures. Many libraries exist for these languages [62] [89] [10], that take advantage of the instructions that hardware can support for implementing high-performance data structures. However, as we move towards many-core architectures, lock-free techniques do not scale well due to mutual exclusion and high contention on memory bus resource.

#### 2.1 Baseline Queue Performance

A single producer single consumer (SPSC) array-based queue provides the lowest latency for enqueue and dequeue operations when both operations do not happen simultaneously since they do not require data synchronization, thread to thread communication and can benefit from data locality. In order to parallelize applications, concurrent queues are necessary for sharing work among various threads and a multiple producer multiple consumer (MPMC) queue is the most commonly used data structure. Thread contention, data synchronization, cache coherence and cache misses are few of the many factors that can highly impact the performance of MPMC queues limiting their scalability.

| Model                   | Sockets-Cores/HT@Freq                                                                                                                                                                                                                                                        |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel Xeon Gold 8160    | 8-192/384@2.1GHz                                                                                                                                                                                                                                                             |

| Intel Xeon Gold 8160    | 2-48/96@2.1GHz                                                                                                                                                                                                                                                               |

| Intel Xeon Gold 6130    | 2-32/64@2.1GHz                                                                                                                                                                                                                                                               |

| Intel Xeon Silver 4110  | 2-16/32@2.1GHz                                                                                                                                                                                                                                                               |

| Intel Xeon Phi 7210     | 1-64/256@1.5GHz                                                                                                                                                                                                                                                              |

| Intel Xeon E5-2620 v4   | 2-16/32@2.1GHz                                                                                                                                                                                                                                                               |

| Intel Xeon E5-2620 v3   | 2-12/24@2.4GHz                                                                                                                                                                                                                                                               |

| AMD Naples 7501         | 2-64/128@2.0GHz                                                                                                                                                                                                                                                              |

| AMD Threadripper 2990WX | 1-32/64@3.0GHz                                                                                                                                                                                                                                                               |

| AMD Ryzen 7 1700        | 1-8/16@3.0GHz                                                                                                                                                                                                                                                                |

| AMD Opteron 6168        | 4-48/48@1.9GHz                                                                                                                                                                                                                                                               |

| POWER9 EP73             | 2-40/160@3.8GHz                                                                                                                                                                                                                                                              |

| ThunderX 88XX ARM v8    | 2-96/96@2.0GHz                                                                                                                                                                                                                                                               |

|                         | Intel Xeon Gold 8160<br>Intel Xeon Gold 8160<br>Intel Xeon Gold 6130<br>Intel Xeon Silver 4110<br>Intel Xeon Phi 7210<br>Intel Xeon E5-2620 v4<br>Intel Xeon E5-2620 v3<br>AMD Naples 7501<br>AMD Threadripper 2990WX<br>AMD Ryzen 7 1700<br>AMD Opteron 6168<br>POWER9 EP73 |

| Table 1         Testbed for evaluation from the Mystic System |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

In order to show the scalability and performance of MPMC queues compared to SPSC queues, we selected five diverse systems (see Table 1) from the Mystic Testbed [85] that represent different architectures with large core counts. The five systems we choose to evaluate for these initial experiments are: 1) AMD Epyc, 2) ARM ThunderX, 3) IBM Power9, 4) Intel Xeon Phi, and 5) Intel Xeon Scalable Processor. More information about these systems (as well as others used in our work) can be found in Table 1.

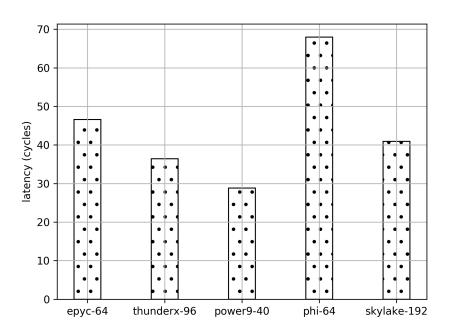

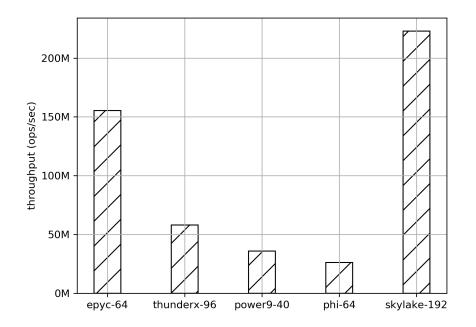

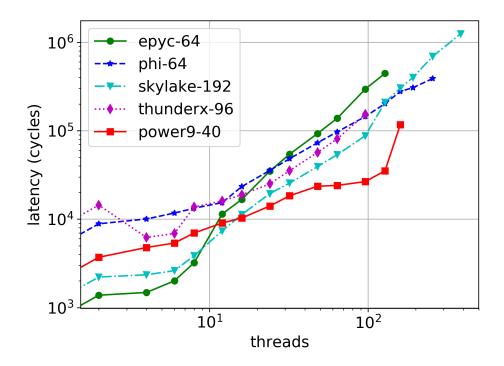

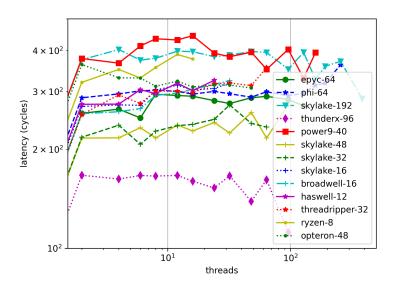

We measured the latency and throughput of a simple SPSC array-based circular queue to identify baseline numbers for the lowest latency that can be achieved on latest many-core architectures. Experiments involve running 1 billion enqueue operations followed by a sequence of dequeues. We measured the latency of each operation and calculated the average time per enqueue/dequeue pair. Queue size is set to the number of samples for the purposes of this evaluation. Results in Figure 2 show the average latency of both enqueue and dequeue operations. It can be noted that latency of any operation on queues takes 30 to 70 cycles depending on the architecture and clock frequency. This latency measurement includes a check if queue is full/empty, an increment operation on head/tail, a modulo operation to ad-d/remove the item. Figure 3 represents the throughput, which is the rate at which items are being processed by the queue. For throughput experiments,

Figure 2 Average latency of enqueue/dequeue operations on SPSC queue

we measured the total time taken for a billion enqueue/dequeue operations and calculated the throughput. Average throughput of enqueue/dequeue operations reaches 270 million operations per second on Intel Skylake 192core machine. Although these results are significant showing excellent single threaded performance, an SPSC queue is limited because it cannot be used with more than one producer and one consumer.

Figures 4 and 5 depict the results obtained by benchmarking a simple multiple producer multiple consumer queue for latency and throughput. The queue is implemented by using a semaphore which keeps track of free spaces in the queue and pthread\_mutex\_lock to lock the queue during enqueue and dequeue operations. This is the most common and simple way to implement a concurrent queue. We do not expect a single concurrent queue with multiple threads to scale well. This experiment aims at quantifying the poor scalability of MPMC queues using mutex locks. Each experiment enqueues and dequeues one billion items using equal number of producer and consumer threads. For all the experiments, a round robin pinning of threads is employed with producer and consumer thread being on the same core and different hyper threads. Binding threads to processor can result in better cache utilization, thereby reducing costly memory accesses. This thread placement is a result of tests performed by pinning producer to core 0 and

Figure 3 Average throughput of enqueue/dequeue operations in millions(M) on SPSC queue

consumer to each other core available and evaluating the performance obtained for every combination which resulted in separate hyper threads on the same CPU giving the highest performance.

Figures 4 and 5 show the latency and throughput, respectively. Our results indicate that latency can reach up to millions of cycles under high contention, and throughput can drop down to as low as 311,329 operations per second (aggregate over all threads). For the skylake-192 system, which had the best single core performance at 270 million operations/sec, the MPMC approach yielded only 810 operations per second per thread at a 384-thread scale (a  $333,333 \times 10$  so f performance). The fastest MPMC queue throughput at any scale reached just 5 million operations/sec. These results provide enough motivation to investigate methods to exploit full concurrency on many-core architectures while not compromising on the lowest latency that can be achieved.

**Figure 4** Average latency of enqueue/dequeue operations on a lock-based queue. This graph is shows that simple lock-based queues don't scale beyond 8 threads on any modern processors.

**Figure 5** Average throughput of enqueue/dequeue operations on lockbased queue. This graph shows that the throughput of a simple lock-based queue plateaus beyond 8 threads on modern processors

#### 2.2 Analysis of Synchronization Mechanisms

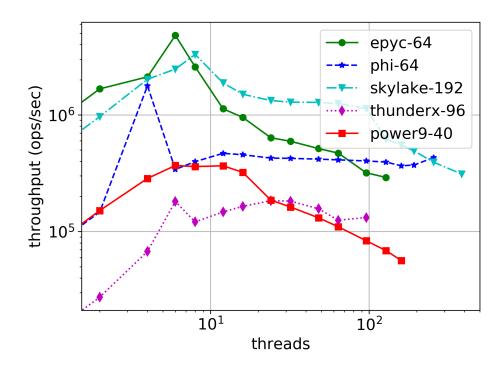

This section conducts a detailed performance study of synchronization mechanisms: 1) mutexes, 2) semaphores, 3) spin locks, and 4) atomic fetch-andadd operations. The evaluation is conducted on a testbed of 13 systems representing today's largest shared-memory systems from Intel, AMD, IBM, and ARM with up to 384 hardware threads.

#### 2.2.1 Tesbed, Software Stack, and Timing Mechanisms

**Testbed:** Table 1 shows details of the testbed used for experiments in this paper. The testbed covers latest many-core architectures from Intel, AMD, IBM and ARM with processors such as Haswell, Broadwell, Skylake, Phi, Opteron, Ryzen, Threadripper, Epyc, Power9, and ThunderX. The smallest system is an 8-core single socket system from AMD. The largest system is an 8-socket system with 24-core Intel CPUs, for a total of 192-cores and 384 hardware threads. The average system scale is about 50-cores and 100 hardware threads.

**Software stack:** All experiments in this paper are performed on Ubuntu 18.04 operating system and compiled using GCC version 7.3 with O2 optimization level.

Fine-grained timing: On x86 architectures, latency is measured in CPU cycles using RDTSCP instruction for start time and RDTSC + CPUID instruction for the end time. RDTSCP is a serializing instruction and it prevents instruction reordering around the call. CPUID is also a serializing call and when it follows RDTSC instruction, it prevents any future instructions to be executed before timing information is read. The combination of these two timing functions gives the most accurate results for latency. Timing on ARM and Power9 architectures is quite different from x86 architectures. ARM processor has a PMU cycle counter which is only accessible in privileged mode. The operating system sets up a virtual counter which counts at the same frequency as the physical counter and can be used for fine-grained measurements. The ARM cycle counter ticks at a lower freguency than the frequency that cores are running at and hence calibration is required to get the multiplier that needs to be applied to the cycle count to get a precise value. In Power9, time base register counts cycles at a fixed lower frequency and needs to be calibrated to convert the value to actual cycles at CPU clock frequency. Throughput in all experiments in this paper is measured using CLOCK\_MONOTONIC for start and end times. Throughput is calculated for each thread individually and all the results are aggregated to get the final throughput value for the experiment.

#### 2.2.2 Performance of Synchronization Mechanisms

In order to program for shared-memory systems using multithreading, threads need to be synchronized. Various thread synchronization mechanisms exist which ensure that threads do not simultaneously execute a critical section of the program. Many languages provide high level abstractions for synchronization to ease parallel programming. Common synchronization mechanisms include mutexes (mutual exclusion locks), semaphores, reader/writer locks and condition variables. Mutex is a mutual exclusion lock which ensures exclusive access to the shared resource. Spinlock is a type of lock which waits in a busy loop if lock cannot be acquired. Atomics operations are instructions supported by hardware and they lock the memory bus to access the shared resource. These operations are inherently atomic and have limited support for data types on various architectures. Semaphores is a type of mutual exclusion where a thread can wait to get access to the critical section or do a post so other threads can get access.

While it is essential to synchronize data between threads, it can easily get very expensive at higher levels of concurrency. This is due to the reason that only one thread can hold exclusive access to the critical section and all other threads are waiting to get the lock using up CPU cycles. Lock-free approaches using atomic operations are believed to be highly efficient, but are hard to implement and maintain. Lock-free algorithms can be implemented by using special hardware primitives such as CAS (compare and swap), FAA (fetch and add) and LL/SC (load-link/store conditional). Most implementations of mutexes are built on top of atomic instructions supported by hardware.

The primary focus here is to analyze the cost of low-level thread synchronization mechanisms and for this purpose, we benchmarked pthread\_mutex\_lock/ pthread\_mutex\_unlock, sem\_wait/ sem\_post, fetch-and-add and spin\_lock/ spin\_unlock to measure latency. Spinlock for this benchmark is implemented using test-and-set algorithm using CAS atomic primitive. Fetchand-add is supported by x86 architectures using 'lock xadd' instruction. The Power9 variant for FAA instruction is 'lwarx/stwcx' and ARMv8 provides

**Figure 6** Average latency of incrementing an integer using different synchronization mechanisms. Same trend is observed on all architectures where latency keeps increasing as threads are scaled up except Intel Xeon Phi.

'ldxr/stxr' which are load/store exclusive instructions used for implementing atomic read, modify, write operations. These benchmarks are obtained by running a tight loop of 1 billion operations and collecting the aggregate of the results. Each iteration acquires the lock, increments a shared integer and releases the lock, excluding fetch-and-add which performs an increment operation atomically.

Figure 6 shows that all synchronization mechanisms exhibit higher latencies due to contention at higher levels of concurrency. There are many factors that impact the cycle counts like cache coherence, communication latency between cores on same and different sockets, interrupts, cache misses, etc. Hence, it is important to run multiple iterations of these benchmarks and to compute the average number of CPU cycles to estimate the latency of these operations. Latency of a single atomic increment on a Skylake system with 192-cores and 384 hardware threads when running on all threads concurrently is 33592 cycles whereas on Intel Xeon Phi Knights Landing with 64-cores and 256 hardware threads, latency reaches 3868 cycles. Similar behavior is observed on other architectures with latencies reaching up to thousands of CPU cycles solely for acquiring the lock, incrementing a variable and releasing the lock.

Although AMD, Intel, ARM and IBM have distinctly different architectures, it is interesting to note that the latency of synchronization mechanisms steadily increases on all the architectures as concurrency increases. For atomic instructions, most architectures show a slow rise in the latency up to 8 threads and latency linearly increases after 8 threads whereas for mutex, spinlock and semaphor, latency steadily goes up as concurrency level increases. Intel Broadwell, Haswell and Skylake processors exhibit similar performance curve as threads are scaled up where as AMD Ryzen, AMD Threadripper and AMD Epyc processors start with a slow increase in latency up to 8 threads for all four types of locks and then the latency rapidly grows as level as concurrency increases.

Intel Xeon Phi Knights landing with 64-cores shows interesting results. Although latency increases up to 64 threads, the latency remains constant as more threads are added. This behavior can be attributed to the round robin hyper-threading implemented in Intel Xeon Phi (which is different than all the other processor architectures evaluated in this paper). In x86 architectures, hyper-threading allows each physical processor to be perceived as two separate logical processors within the operating system by sharing the resources, which results in both hyper-threads running simultaneously increasing contention on each core. Whereas, in Intel Xeon Phi, every core alternates scheduling hardware threads at each cycle thereby not increasing contention and resulting in a better performance as threads are scaled up to more than the number of cores [106].

#### 2.3 Conclusion

We were not surprised by these findings as it is well known that state-of-theart synchronization mechanisms do not scale beyond single digit concurrent threads [79]. These limitations are automatically imposed onto concurrent data structures that are implemented using such synchronization mechanisms. Furthermore, use of such concurrent data structures in modern parallel runtimes have significant overheads for managing extremely finegrained tasks. Even though at low concurrency these mechanisms only cost hundreds of cycles, these costs quickly grew to tens of thousands and even hundreds of thousands of cycles at hundreds of threads. Our experience with the cost of synchronization mechanisms at high concurrency along with the cost of MPMC queues as a building block for parallel runtimes has motivated our investigation into methods to eliminate synchronization mechanisms in order to unleash the full performance of many-core architectures under high concurrency.

# CHAPTER 3

## Scalable Concurrent Queues on Modern Many-core Architectures

This work is motivated in large part by the significant latency gap observed with SPSC and MPMC models.

A simple concurrent SPSC queue can enqueue and dequeue items in less than 100 cycles. Independent SPSC queues per core could, in theory, scale linearly with increasing core counts. Thus, we believe that an MPMC lock-less queue can be built using SPSC queues by manipulating the task/data flow carefully.

We introduce XQueue, a novel lock-less MPMC, out-of-order queuing mechanism that can scale up to hundreds of threads. XQueue uses B-queue [116] as a building block. B-queue is a concurrent SPSC lock-free queue designed for efficient core-to-core communication. It is implemented without using any locks, atomic operations, or barriers. The latency of queue operations in B-queue is as low as 20 cycles. B-queue uses batching where both producer and consumer detect a batch of available slots that are safe to use. Batching avoids shared memory access and therefore improves performance. Several fast SPSC queues have been proposed in recent years [75, 71, 5] and we aim to demonstrate that XQueue can be built with any fast and scalable SPSC queue.

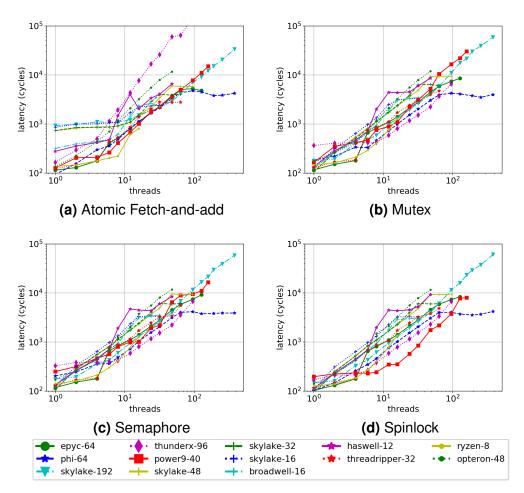

**Figure 7** Architecture of XQueue on a 4-core machine with 4 queues per consumer.

Figure 7 shows the architectural of XQueue on a 4-core system. The key idea here is to have N SPSC concurrent queues per worker if there are N workers. There is one master queue and N - 1 auxiliary queues per worker, with N (equal to number of workers) producers adding items into master queues. Every item is a void pointer that represents a task where a task could be a function pointer or data pointer. One worker exists for dequeueing tasks from the master queue as well as the auxiliary queues. A worker first tries to dequeue a task from the master queue. If a task is dequeued successfully, it is processed immediately. The item when processed can generate one or more items to be enqueued into the auxiliary queues of the other CPU cores. Every worker distributes work to auxiliary queues in a round-robin fashion as shown in Figure 7. A worker then tries to dequeue an item from its auxiliary queues and dequeued items are processed immediately.

A simplified version of pseudocode for worker logic is outlined in Algorithm 1. Since all queues in XQueue are concurrent SPSC queues, producer and consumer threads can act concurrently processing items in the queues. The strategy of distributing work across queues (as shown in Figure 7) ensures that there is a only a single producer and single consumer for every queue at any point in time. Due to this design, locks can be completely avoided thereby reducing the latencies of queue operations and improving overall performance.

#### Algorithm 1 Worker logic.

$id \leftarrow coreId; next \leftarrow nextCoreId;$

while 1 do  $ret \leftarrow dequeueFromMaster(id, item);$

if ret = SUCCESS then  $retItem \leftarrow processItem(item);$

if  $retItem \neq NULL$  then enqueueToAuxiliary(next, retItem); $ret \leftarrow dequeueFromAuxiliary(id, item);$

if ret = SUCCESS then  $retItem \leftarrow processItem(item);$

if  $retItem \neq NULL$  then enqueueToAuxiliary(next, retItem); $next \leftarrow (next + 1)\%numCores;$

if next == id then next++;

#### 3.1 Load balancing

In most parallel programming systems, it is a common scenario to use multiple queues, one per worker, with work produced and consumed locally by the workers/threads. Load balancing is commonly achieved by using techniques like work stealing [31, 45]. While XQueue also uses multiple queues, it balances load by the virtue of its design with N queues per core and consumer threads inserting items into the auxiliary queues of all the other cores. This architecture enables distribution of task graphs to multiple threads with minimal overhead due to the lock-less design as compared to the stateof-the-art work stealing techniques which primarily use locks or atomics to achieve synchronization.

In a task-parallel program, tasks can be modeled as a Directed Acyclic Graph (DAG) which can be traversed based on inter-dependencies between the tasks. Task graphs have a pool of ready tasks which can be processed by threads and subtasks can be generated. The master and auxiliary queues and the communication between them is modelled after the dynamic execution of a program where a task can generate subtasks. In the case of XQueue with N workers and N queues per worker, as shown in Figure 7, we employ a ring buffer topology for communicating between queues. Essentially, the consumer thread of every set of queues acts as a producer thread of N - 1 auxiliary queues of all the other threads. This pattern of tasks distribution ensures optimal load balancing in terms of the number of tasks

processed per worker. However, this may not be the best fit for every scenario for various reasons, such as data locality, task dependencies, and per task execution time. Optimal allocation of work among various threads is known to be NP-hard, but, in the case of XQueue, depending on the nature of work, the topology of connections between queues and task distribution strategy can be changed to achieve best performance.

The load balancing mechanism in XQueue can be considered as a pushbased mechanism as opposed to pull-based work stealing approach. This primary difference impacts how initially imbalanced workloads are handled. For example, consider the case of Fibonacci. Execution starts with a single task which recursively unfolds the DAG as execution progresses. In the work stealing approach, idle workers randomly try to steal tasks from other workers. This results in several failed steals and coupled with the cost of locking for every steal, incurs significant overhead. On the other hand, the push-based approach of XQueue handles this efficiently with its round-robin distribution without the use of locks, thus incurring minimal overhead. We discuss the advantages and disadvantages of this approach in Section 3.4.

On modern many-core architectures, it is common to have multiple Nonuniform memory access (NUMA) zones which impact the latency of memory operations from various cores. In XQueue, every worker allocates queues in its respective NUMA zone. This ensures that any memory reads and writes from various threads have the lowest latency possible. However, when tasks propagate through auxiliary queues in the system, the latency of memory read/write is higher across NUMA zones. With XQueue's ring buffer design across N cores with N queues, some latency is unavoidable due to the underlying architecture.

In summary, there is a lot of flexibility for defining the topology for task distribution statically and dynamically during program execution with XQueue. If the nature of the DAG and data access patterns are known, the task distribution can be tuned to achieve best performance as compared to state-ofthe-art work stealing approaches.

#### 3.2 Xtask - eXtreme fine-grained TASKing runtime

XQueue is designed to have the lowest latency of operations since it does not use any locks or atomic operations for synchronization. XQueue achieves minimal load balancing automatically as execution progresses and depending on the nature of the DAG and size of tasks, applications with balanced DAG will benefit from using XQueue as the underlying data structure for managing tasks. To demonstrate this, we developed a prototype parallel runtime system that can process a dynamic task graph with task dependencies. The runtime system employs a producer consumer architecture. Underlying data structure to hold the bag of tasks is XQueue which is implemented using multiple single producer single consumer queues as describe earlier in this section. Number of producers and consumers is configurable at runtime along with the queue sizes. A pool of worker threads are launched waiting to consume tasks from multiple gueues. When the framework bootstraps, it allocates memory for the queues on the NUMA node where the thread is created on. The framework uses pthread library for implementing multithreading. We originally developed Xtask wit a long-term goal to accelerate fine-grained parallel applications implemented in OpenMP, OpenCL, Swift/T, etc orders of magnitude beyond the state-of-the-art. However, it guickly became evident that it is cumbersome to implement complex applications using the Xtask API since the applications have to be broken down into tasks manually and rewritten. OpenMP is a popular standard for implementing parallelism by decorating the code with pragmas. We decided to integrate our ideas into OpenMP in order to broaden the scope of our ideas into real applications.

#### 3.3 XQueue Integration with the OpenMP Runtime

In order to extend our research to real systems, we integrated XQueue into OpenMP [14] to enable execution of unmodified OpenMP programs using XQueue. OpenMP's tasking model provides a way to efficiently parallelize dynamic task graphs and recursive algorithms. Several implementations of OpenMP exist: GNU OpenMP (for GCC) [101], LLVM OpenMP [14], and Intel OpenMP. We chose to integrate XQueue into the LLVM OpenMP due to its open source code and its superior performance as compared to GNU OpenMP with fine-grained tasks [86].

**Implementation:** In the LLVM OpenMP tasking implementation, every thread owns a queue and the enqueue/dequeue operations are protected by locks implemented using Lamport's bakery algorithm. We replaced the task queues in OpenMP with multiple SPSC queues per worker to model XQueue. OpenMP implements a work-stealing scheduler. Every thread first checks it's own queue for tasks. If no tasks are found, a thread is randomly chosen to steal

a single task. We replaced the work stealing scheduler with the scheduler for XQueue as shown in Algorithm 1. In our XQueue-based OpenMP implementation, every thread checks it's own queue for tasks. If no tasks are found, the scheduler checks all auxiliary queues. This process of checking the master queue and auxiliary queues is repeated until a termination condition is satisfied.

**Optimizations:** We applied few optimizations to the XQueue system during integration with the OpenMP runtime. Since the core design of XQueue is to have multiple queues per worker, at higher thread counts (hundreds), the latency of checking all auxiliary queues can become significant and reduce the overall performance. To solve this issue, we implemented a hinting mechanism where every producer stores the ID of the last queue to which the task was pushed. This hint can possibly be over-written by multiple threads writing to various queues, however this simple mechanism reduces the latency of checking auxiliary queues many times.

#### 3.4 Performance Evaluation

We evaluate the performance of XQueue using synthetic and real workloads. For the purposes of evaluating XQueue independently, we developed a prototype parallel runtime system that can process a dynamic task graph with task dependencies using XQueue. We first evaluate XQueue individually using a series of micro-benchmarks. We deployed XQueue on 13 systems (Table 1); we then picked the system with the highest number of cores, the skylake-192 with 192-cores and 8 NUMA zones to conduct deeper analysis.

#### 3.4.1 Experiment Setup

We implemented three systems for the micro-benchmark evaluation:

- (1) **XQueue (SPSC)** uses a single SPSC queue per worker.

- (2) **XQueue (MPMC)** uses an MPMC queue with a master queue per worker.

- (3) **XQueue (Cilk Deque)** uses a Cilk deque [38] with a separate queue per worker.

Cilk deque is implemented as part of Cilk 5 multi-threaded language [38] and uses a shared-memory, mutual-exclusion protocol called the THE protocol[30] for implementing locks. This mechanism of locking is about 25% faster than hardware locking primitives.

For the macro-benchmarks, we use the XQueue-enabled LLVM OpenMP implementation with N queues per worker and N workers. We compare it with the native LLVM OpenMP and GNU OpenMP libraries.

#### 3.4.2 Micro-benchmark Performance Results

In each experiment we perform 1 billion enqueues/dequeues concurrently by varying the number of threads. We consider a single operation to be the act of dequeing an item from the master queue and executing the function to which that item points to. The function performs a single NOP operation. The X-axis on all the figures represents the number of producers/consumers.

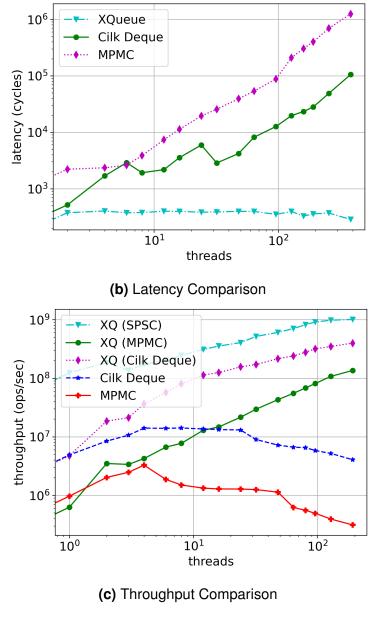

Figure 8a shows the latency of queue operations on XQueue using lockless queue. Each queue operation takes around 110 to 400 CPU cycles on average on all architectures considered. ARM ThunderX shows the lowest latency and IBM Power9 shows the highest latency in these microbenchmarks. Intel processors Skylake, Haswell, Broadwell and Xeon Phi show latencies in the range of 180 to 300 CPU cycles on average. The standard deviation is low across all architectures indicating that XQueue with lock-less queue can scale up to hundreds of threads with latencies as low as 110 to 400 cycles.

Figure 8b compares the latency of XQueue (SPSC) with Cilk Deque and MPMC queues on skylake-192. Here, Cilk Deque/MPMC is a single queue shared across all the workers. With 192 producers/consumers, latency of MPMC queue is  $13 \times$  the latency of Cilk deque. Cilk deque's Dijkstra-like locking mechanism achieves much lower latency than locks implemented using hardware locking primitives. However, the latency is much higher compared to XQueue which does not use any locks. It is noteworthy that XQueue has relatively constant latency as we increase the number of threads by two and half orders of magnitude, while Cilk deque and MPMC show significant latency increases over the same scale.

(a) Average latency of enqueue/dequeue operations using XQueue (SPSC)

Figure 8 XQueue Performance on Skylake-192

Figure 8c is a log-log plot showing the throughput of XQueue using lockbased and lock-less queues on the skylake-192 system. The throughput achieved on this system with XQueue with lock-less queue is 1 billion operations per second with all hyper threads being utilized. For XQueue using lock-based gueue, the average throughput achieved is 200 million operations per second and 397 million for the Cilk deque. In the case of MPMC queue, each mutex lock is held for short intervals and contention is low, but acquiring the lock has a cost which explains the  $5 \times$  gap in performance as compared to XQueue with lock-less queue. Cilk deque also incurs a cost for acquiring and releasing the lock (a  $2.5 \times$  gap), although the cost is lower compared to mutex-based locks. Similarly XQueue implementations over both lock-less and lock-based queues highly benefit from data being in the cache avoiding costly memory accesses. A single lock-based queue shared among all threads shows improvement in performance up to a maximum of 8 threads on all architectures and it steadily declines as more threads are added. As noted in Chapter 2 for MPMC gueue, with high contention on the mutex lock with more than 8 threads, throughput drops to about 300K operations per second on skylake-192 with 384 threads. In case of Cilk deque, the throughput drops to 4 million operations per second. This clearly shows a 3300X gap in throughput between XQueue with lock-less queue and single lock-based queue with hundreds of threads.

The results obtained from micro-benchmarks using XQueue with lock-less queue and lock-based queue are significant and show that this architecture can scale to at least hundreds of threads with any scalable concurrent SPSC queue implementation. It can be noted that these micro-benchmarks do not take into consideration the cache effects of task distribution to other cores in XQueue since there are no auxiliary queues. Hence, this benchmark shows the lowest latency and highest throughput that can be achieved, providing a baseline.

#### 3.4.3 Macro-benchmark Performance Results

To quantify the improvements in real application workloads, we evaluate the speedup achieved using XQueue-enabled LLVM OpenMP as compared to the native LLVM OpenMP and GNU OpenMP libraries. We evaluate five out of nine applications from the BOTS benchmark suite [36]: Fibonacci, FFT (Fast Fourier Transform), Multisort, NQueens and Health. Results are shown in Figure 9. We also evaluate the breadth first search application

from the GAP benchmark suite [12] with real-world social network graphs such as those from Friendster and Twitter. Results are shown in Figure 11. The application workloads are summarized in Table 2.

| Application | Inputs(S,M,L,XL)     | Highest Task Count |

|-------------|----------------------|--------------------|

| Fibonacci   | 44, 46, 48, 50       | 40.7B              |

| FFT         | 134M, 268M, 536M, 1B | 128M               |

| Multisort   | 134M, 268M, 536M, 1B | 14M                |

| Nqueens     | 14, 15, 16           | 1.1B               |

| Health      | small, medium, large | 126M               |

| BFS         | friendster           | 79M                |

| BFS         | twitter              | 40M                |

**Table 2**Application - number of tasks

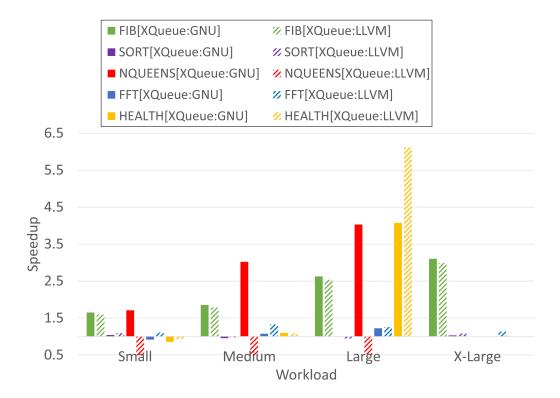

**Fibonacci (Fib)** computes the Nth Fibonacci number using recursive parallelism. While Fib is hardly a critical parallel application, it *does* have extremely fine-grained tasks (e.g., addition of two numbers) with extremely large number of tasks, and thus exposes the limits of a tasking runtime in terms of granularity. Figure 9 shows the results obtained on skylake-192. OpenMP with XQueue achieves  $3 \times$  speedup as compared to the native LLVM and GNU versions for Fib(50). The performance gap increases with problem size due to the increase in overhead of locking operations in the native OpenMP versions with more fine-grained tasks. Further analysis using Intel Vtune Profiler showed that about 50% of the execution time is spent in these operations which includes waits and atomics, where as this overhead is negligible in the XQueue version due to the lack of locks or atomics. The overall runtime overhead for managing fine-grained tasks of this application reduced from over 90% to 29% of the CPU time when using XQueue.

**Multisort** sorts 32-bit randomly generated numbers using a fast parallel sorting variation of mergesort. It uses a recursive algorithm with a base condition of 2048 numbers and they are sorted using serial quicksort and insertion sort is used for arrays with less than 20 elements. The application scales well up to 96 threads for all the runtimes and XQueue is faster for all problem sizes with 1.97× speedup for the largest problem size. However, the performance drops by 50% at 192 threads. As shown in Figure 9, XQueue achieves similar performance compared to LLVM and GNU versions using 192 threads. LLVM and GNU versions of OpenMP exhibit high CPI (cycles per instruction) rate (0.5 for XQueue vs 24 for both LLVM and GNU for the largest problem size) which is the result of waits, atomics, and locks in the GNU/LLVM versions. However, since this application is heav-

ily memory-bound, the benefits of avoiding locks and lower CPI in XQueue are outweighed by the data movement across cores, thereby resulting in no performance benefit.

**Health** simulates the Columbian Health Care System [29]. A list of potential patients in a village with one hospital are simulated with several possibilities of getting sick, needing treatment or reallocating to an upper level hospital. Every village being simulated is run as a task. The different probabilities at each step cause indeterminism and load imbalance. On skylake-192, the performance of this application is heavily impacted due to remote memory accesses for moving the village data across NUMA zones. Despite some load imbalance, XQueue achieves  $6 \times$  speedup compared to LLVM variant and  $4 \times$  speedup compared to GNU variant using the large input data.

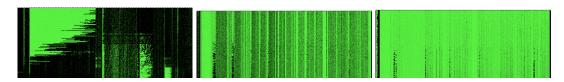

**Fast Fourier Transform (FFT)** computes the 1D FFT of a vector with N complex values using the Cooley-Tukey Algorithm. This algorithm recursively divides the FFT into several smaller Discrete Fourier Transforms (DFTs) creating multiple tasks at each step. Although the XQueue version has the advantage of reduced overhead due to lock-less queues, the task distribution suffers due to the static round-robin placement of tasks resulting in similar overall execution time as compared to other versions of OpenMP. Figure 10 shows the timeline view of the OpenMP parallel region for the largest problem size, where green represents effective work and black represents the spin/wait/overhead time introduced by load imbalance. It is noteworthy that OpenMP with XQueue with worse load balancing can still achieve slightly improved performance (between  $0.9 \times$  to  $1.2 \times$ ) due to the smaller overheads incurred by avoiding locks.

**NQueens** computes all the solutions for placing *N* queens on an  $N \times N$  chess board such that no queens can attack each other. The algorithm prunes certain branches of the tree that cannot reach the solution which creates load imbalance. Figure 9 shows that the XQueue-enabled OpenMP implementation achieves 4X speedup compared to the GNU version. The performance loss in XQueue as compared to standard LLVM is due to the significant load imbalance. On the other hand, GNU OpenMP incurs huge synchronization overheads for managing fine-grained tasks (about 60% on skylake-192) and the performance is significantly lower for GNU OpenMP compared to OpenMP with XQueue.

**Figure 9** Speedup of XQueue over standard GNU and LLVM OpenMP implementations on the BOTS benchmarks on skylake-192 using 192 threads.

**Figure 10** Load balance of FFT on skylake-192 - LLVM+XQueue (left), Native LLVM (middle), GNU(right)

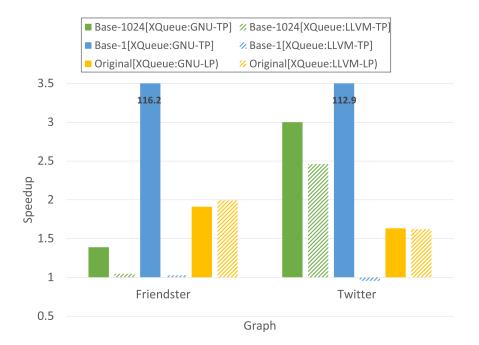

**Breadth First Search (BFS)** is a fundamental building block of many graph algorithms: it checks the connectivity of the graph from given source vertices, visiting one layer at a time. In order to demonstrate the applicability of XQueue using real-world datasets, we evaluate the BFS application from the GAP Benchmark Suite [12] using social network graphs such as Twitter and Friendster. The original implementation of BFS in the GAP benchmark leverages loop parallelism (LP) to parallelize every level of the tree. We modified the code to use recursive task-based (TP) parallelism with a base condition of 1024 nodes to evaluate XQueue. We also evaluate the extreme case with a base condition of 1 node, which creates several extremely finegrained tasks. Each data point is the average speedup obtained by running BFS 64 times from pseudo-randomly selected non-zero degree source vertices. The Twitter graph has 61 million nodes and 1.47 trillion directed edges for a degree of 23 where degree is the maximum number of edges connecting a vertex. The Friendster graph has 65 million nodes and 3.61 trillion directed edges for a degree of 55.

Figure 11 shows the speedup achieved for both the test graphs on the skylake-192 using 192 threads. For the Friendster graph with a base case of 1024 nodes, GNU OpenMP scales well up to 24 threads and performance degrades at higher concurrency levels. XQueue performs reasonably well at full scale of 192 threads as compared to GNU and LLVM. XQueue achieves a speedup of  $1.4 \times$  for Friendster and  $3 \times$  for Twitter graphs over GNU with base case of 1024 nodes. Execution times for LLVM and XQueue are similar for Friendster and for Twitter, XQueue achieves  $2.4 \times$  speedup. For the base case of 1 node, while there is no significant performance difference between LLVM and XQueue, GNU's performance suffers significantly (up to  $116 \times$  slower) due to the overhead of managing fine-grained tasks. Since real social network graphs are very unbalanced, they result in highly irregular memory accesses and load imbalance. Compared to the original GAP BFS using loop parallelism, XQueue achieves 1.9× speedup using Friendster and  $1.6 \times$  speedup using Twitter with 192 threads, showing promise that the task-based parallel approach can be beneficial for these types of workloads.

Overall, our results show that there is significant room for improvement in existing task-parallel runtimes and higher performance can be achieved by using lock-less techniques. Improving load balancing could yield further performance improvements similar in size to the improvements seen here.

**Figure 11** Speedup of XQueue over standard GNU and LLVM OpenMP implementations when applied to Breadth First Search from GAP Benchmark Suite on skylake-192 using 192 threads.

#### 3.5 Conclusion

XQueue is an extremely scalable lock-less MPMC out of order queuing system which can be used in tasking runtimes to overcome the performance limitations due to overhead of synchronization. Evaluation results show that XQueue is scalable up to hundreds of threads of execution with up to  $6900 \times$  lower latencies and  $3300 \times$  higher throughput when compared to naive implementations. We integrated XQueue with LLVM OpenMP and were able to achieve up to  $6 \times$  speedup compared to native LLVM OpenMP and  $1 \times$  to  $4 \times$  speedup compared to GNU OpenMP in most cases with up to  $116 \times$  speedup in some cases on applications from the BOTS benchmark suite and BFS application from the GAP benchmark suite.

# CHAPTER 4

# X-OpenMP – eXtreme fine-grained tasking using lock-less work stealing

We introduced XQueue, a lock-less concurrent queueing framework for task parallel runtime systems which enables extreme fine-grained task parallelism. This is achieved by reducing the overheads of the underlying concurrent data structures used in runtime systems. We demonstrated performance improvements that could be obtained on modern architectures with hundreds of cores using several benchmarks. However, XQueue framework relies on a static round-robin load balancing strategy for distributing work across processors. While this approach to push work eagerly to other workers can achieve modest load balancing, the lack of dynamic load balancing can severely limit the performance of real-world workloads.

Load balancing is crucial to parallel applications as imbalances quickly lead to sub-optimal execution times. Work stealing is typically used in most parallel runtimes and execution models for load balancing. Work stealing involves stealing work from a random busy worker when a processor runs out of work. Traditional work stealing implementations use lock-based approaches to steal work from concurrent queues. These concurrent data structures do not scale up to hundreds of threads on modern many-core architectures and exhibit significant overheads at high levels of concurrency. Acar et al. explored a lock-less approach for work stealing by implementing an algorithm that can steal work non-atomically [2]. We extend their work on load balancing along with our prior work on lock-less concurrent parallel framework [80] and propose a dynamic lock-less load balancing mechanism that can provide significant performance improvements using real application workloads.

#### 4.1 Motivation

In task-parallel runtimes, load imbalance is a significant performance limiting factor. Several studies have shown the importance of dynamic load balancing in multi-threaded applications [31, 6]. Dynamic load balancing enables better distribution of work across the processors to achieve efficient performance. In a multi-threaded runtime, typically tasks are executed by a fixed number of workers. Every worker owns a task pool and execute tasks from their pool. Any subtasks that are spawned are inserted into the worker's own task pool. When a worker runs out of tasks, it randomly picks workers to steal tasks from. The amount of load balancing required varies from application to application. Workers can steal a single unit of work at a time, or two units, or half the amount of work from the victim's task pool. Literature has shown that asking two random workers for work is sufficient in most cases to achieve exponential improvement in performance [76].

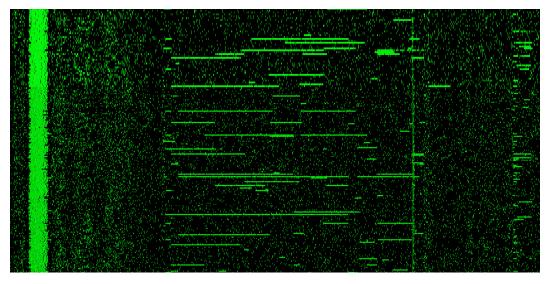

Figure 12 shows the timeline plot of the Unbalanced Tree Search (UTS) benchmark [83] executed using GNU's implementation of OpenMP. The green dots indicate effective CPU time and the black dots indicate idle time. The plot shows a significant load imbalance for this application where several workers (bottom of the figure) are idle for most of the application run, and other workers are idle for a significant amount of the time. The load imbalance results in a major slowdown in the execution time of the application. The UTS benchmark is designed to understand the efficiency of dynamic load balancing in parallel runtime systems and this plot clearly highlights the imbalance in existing task-based runtime systems. Processors are heavily under-utilized resulting in poor overall performance. The simplest way to achieve load balancing is to distribute work across workers in a round-robin fashion. While this is easy to implement, real-world applications are dynamic in nature with varying computational intensity and complexity. A naive round-robin load balancing approach may not be sufficient for improving the performance of real-world workloads [13].

**Figure 12** Load Imbalance in Unbalanced Tree Search using 192 threads and GNU OpenMP

Multi-threaded systems use synchronization mechanisms like mutexes, semaphores, spinlocks, or atomic operations [105, 59] to ensure thread safety and correctness. Concurrent data structures are the central building block of multi-threaded execution models and work stealing relies heavily on these implementations. However, traditional synchronization mechanisms do not scale to hundreds of threads. The mutual exclusion required to ensure correctness, consistency, and thread safety leads to serialized concurrent accesses and adds unnecessary overheads. New approaches for concurrent data structures are necessary to push the limits of scalability on modern many-core architectures. Lock-free approaches [93, 24, 73, 72, 74] mitigate these overheads to an extent by using atomic operations which guarantee system-wide progress, but literature has shown it is very difficult to write correct lock-free code [100]. Lock-less non-atomic updates to data structures are significantly faster compared to the atomic variants and are the focus of our work.

One of the challenges of parallel execution models that use traditional work stealing is the potential need for a large number of steals to achieve optimal load distribution. When a runtime is initialized and workers are created, they start looking for work and when no work is found in the local task pool, work stealing is triggered. Studies have shown that several steal requests are generated at the beginning and tail end of the execution [117]. Work stealing implemented using traditional synchronization-based mechanisms tend to have huge overheads for stealing work. Hence, work stealing should be triggered sparingly and only when necessary to avoid unnecessary overheads.

#### 4.2 X-OpenMP - eXtreme fine-grained tasking runtime

OpenMP is a popular standard for implementing parallel runtime execution models. Task-based parallelism has emerged for exploiting dynamic parallelism from applications on modern many-core and multi-core architectures. We introduce X-OpenMP with the goal of enabling extreme fine-grained parallelism for task-parallel applications. We extend our work on XQueue and implement dynamic load balancing to overcome the limitations of static round-robin load balancing.

#### 4.2.1 Load Balancing

Static round-robin load balancing is limited for dynamically unfolding task graphs due to the inability to load balance during the course of application execution. Most multi-threaded runtime systems [38, 23, 104] use load balancing mechanisms like work stealing and work sharing in order to reduce the overall execution time. Traditional work stealing mechanisms typically use synchronization constructs to safely steal work from the victim's queue. However, since XQueue uses SPSC queues where queue operations are not protected using locks, there is a need to design a lock-less algorithm that can perform dynamic load balancing of tasks using work stealing.

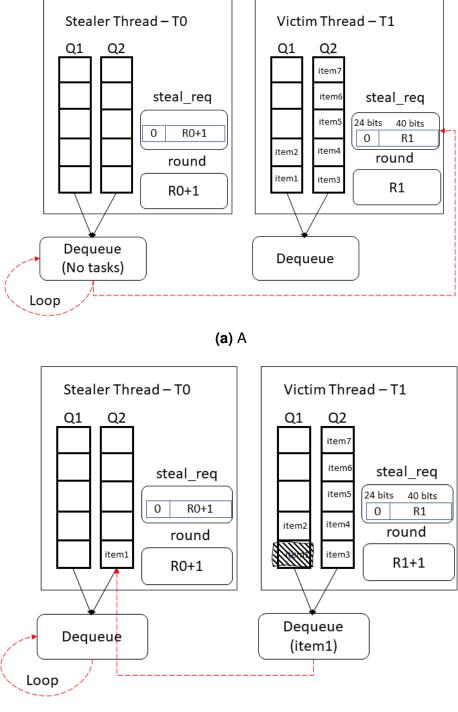

#### 4.2.1.1 Lock-less Work Stealing Using Wait

A mechanism that does not use synchronization is required for implementing work stealing using XQueue. Intel's x86 architectures have a memory model that supports Total Store Ordering (TSO) [96]. TSO guarantees that load and store operations to a memory location are in order as issued by the processor. This memory consistency model provides an opportunity to explore lock-less techniques on x86 architectures for implementing low overhead concurrent data structures and load balancing mechanisms. Prior work has presented an algorithm that does not require atomic read-modifywrite operations for shared memory work stealing [2] that works on total store memory architectures like Intel's x86. Processors communicate by reading and writing into memory locations non-atomically. The details of the original implementation can be found in the technical report [2]. We employed a modified version of this algorithm for work stealing in X-OpenMP to implement dynamic load balancing. The implementation works as follows. The algorithm requires two memory cells per worker where one cell holds a combination of 40-bit round number (representing the round of work stealing) and 24-bit identifier (ID of the worker) packed into a 64-bit word and the other memory cell holds a pointer to the stolen task. Algorithms 2 and 3 present the pseudocode for victim and stealer threads. To perform work stealing, an idle thread (stealer) first randomly picks a victim. As shown in Algorithm 3, the stealer first checks if the victim is accepting requests. This is shown in the first line of the algorithm where the 40-bit round number is extracted by using bit operations and compared with the victim's own round number. The steal request is valid only if the extracted round number is less than the victim's own round number. The stealer then takes a copy of victim's round number and writes its identifier packed with the round number into the victim's 64-bit memory cell. The stealer thread waits in a while loop until the copy of its round number matches the victim's round or a stolen task is received. While waiting, it also writes a steal request to it's own memory cell and leaves it unserved. This self query makes sure no other steal requests come in to this thread since it is idle. When a stolen task is copied by the victim to the stealer's memory cell, the stealer immediately breaks out of the while loop and executes the task. On the other hand, a busy victim looks at it's memory cell during a dequeue operation, as shown in Algorithm 2, extracts the round number from the steal request and compares this round number with its current round number. If it matches, the steal request is valid and the victim dequeues a task from its queue and copies it to the stolen task memory cell of the stealer. The victim increments it's round number to invalidate any steal requests coming in. The round is incremented in 2 scenarios: (1) when a steal request is served and a task is copied to the stealer's stolen task field; and (2) when victims' queues are empty.

The pseudocode presents only the core logic leaving out the complex implementation specific details. The actual implementation also ensures that a stealer is not able to steal requests from other threads while it is waiting to steal a task. Also, this implementation works similarly to traditional work stealing mechanisms where a stealer waits to steal a task from a victim.

The original algorithm in the technical report [2] is implemented for stealing threads and waits forever in the while loop until a steal succeeds or is Algorithm 2 Work Stealing With Wait - Victim's Logic  $local\_steal\_req \leftarrow thread-> steal\_req; round \leftarrow local\_steal\_req \&((1 << 40) - 1);$

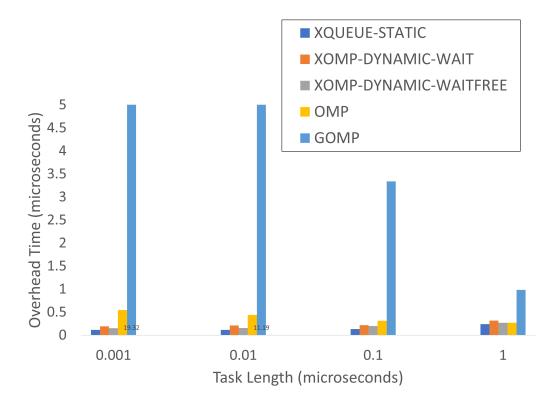

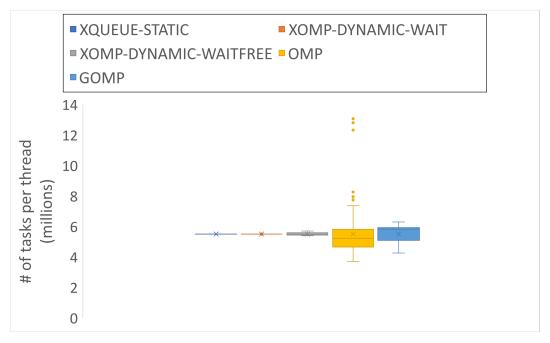

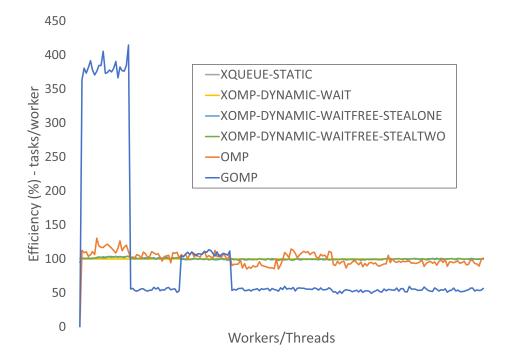

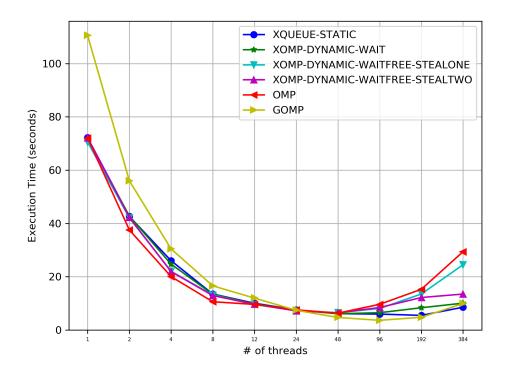

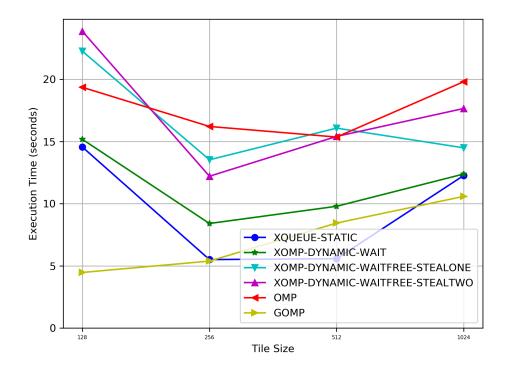

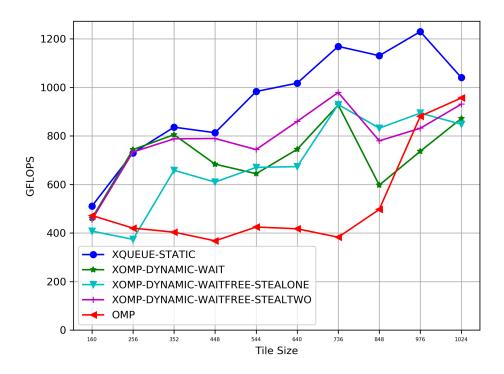

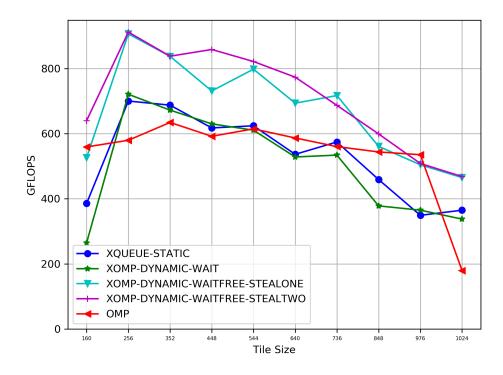

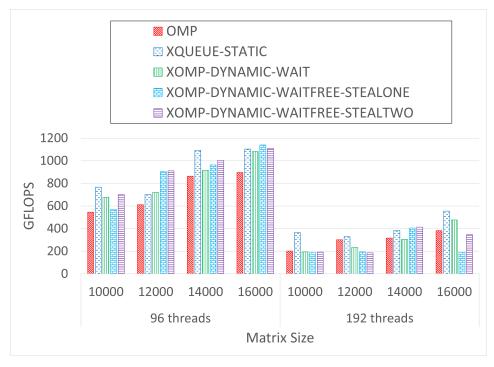

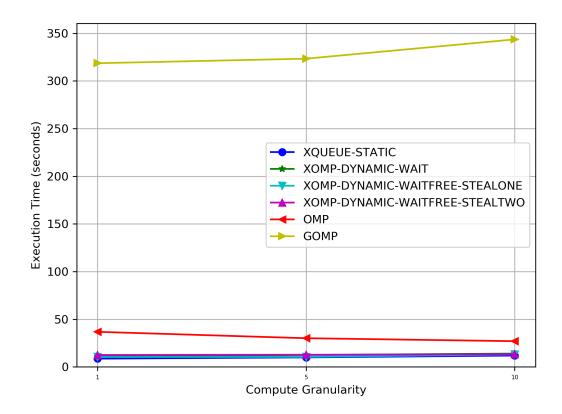

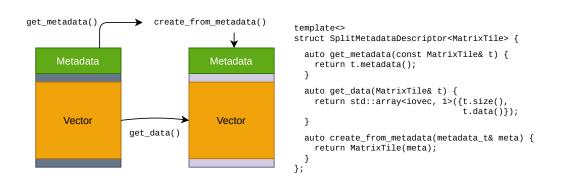

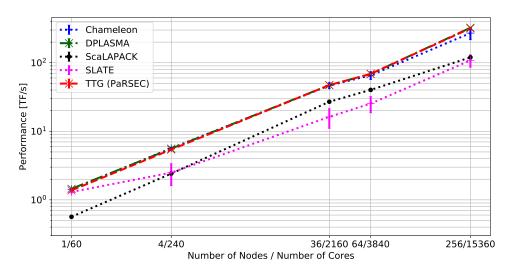

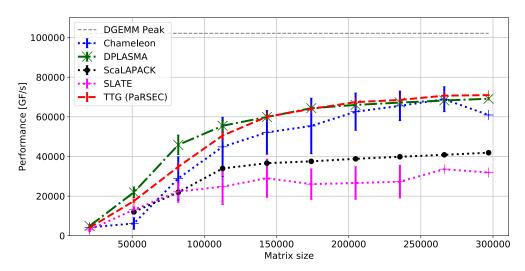

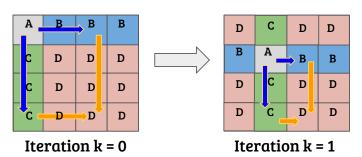

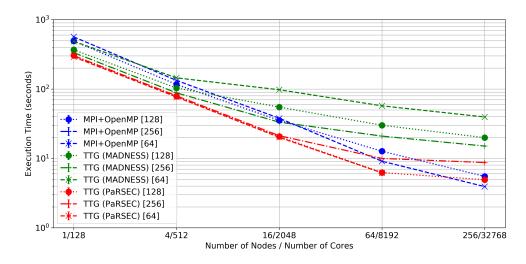

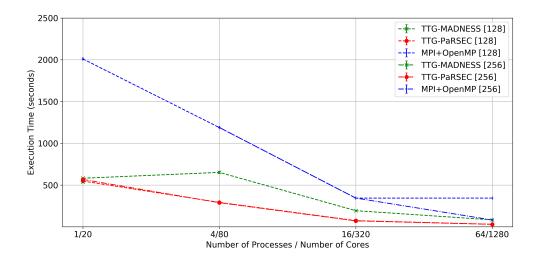

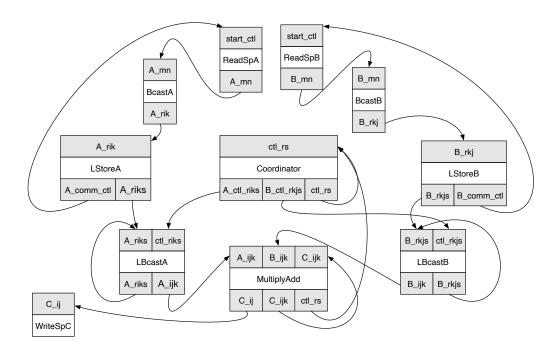

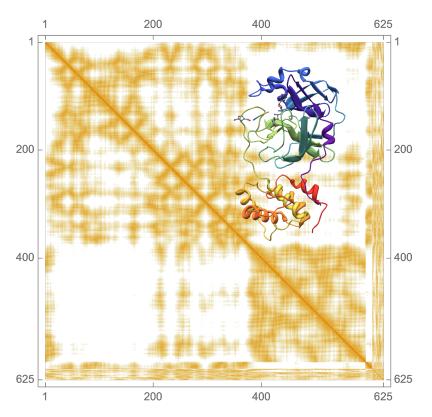

if round == thread - > round then  $ret \leftarrow dequeue(thread_id, item);$